CX-Card5 Rev2.0の変更点

1.FPGA I/Oバンク電源回路の変更

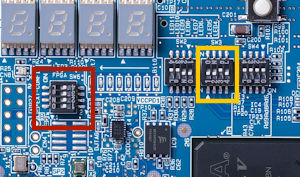

左画像の黄枠内がVCCIO電圧設定用DipSWです。Rev2.0では、4bitすべてOFFまたは、いずれか1bitだけONにする設定です。製品出荷時はbit3だけONなので、2.5V設定です。

赤枠内のDipSWはRev2.0で追加したVCCPD電源選択用です。 黄枠DipSWのbit4=ON(3.3V設定)のときだけ、赤枠DipSWのbit2をONにします。

| I/O電圧 | DipSW[1] | DipSW[2] | DipSW[3] | DipSW[4] |

| 1.2V | OFF | OFF | OFF | OFF |

| 1.5V | ON | OFF | OFF | OFF |

| 1.8V | OFF | ON | OFF | OFF |

| 2.5V | OFF | OFF | ON | OFF |

| 3.3V | OFF | OFF | OFF | ON |

※製品出荷時状態ではVCCIO=3.0V設定ができません。

1608サイズのチップ抵抗を付け替えることで対応できます。

詳細はボードマニュアルを参照してください。

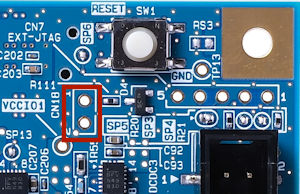

2.外部リセット端子の追加

ボードを筐体に収容したときなど、筐体パネルに備えたリセットボタンからの配線を以下画像の赤枠内に接続し、システムリセットすることができます。2.54mmピッチ 2ピン。

基板仕様の変更

- 基板色を赤から青に変更

- 基板表面処理を金フラッシュに変更