ラズパイCM4とPCIe接続するFPGAにAXIバスシステムを構築して、簡単にFPGA-IOの制御やFPGAに繋がるHyperRAMを制御します。

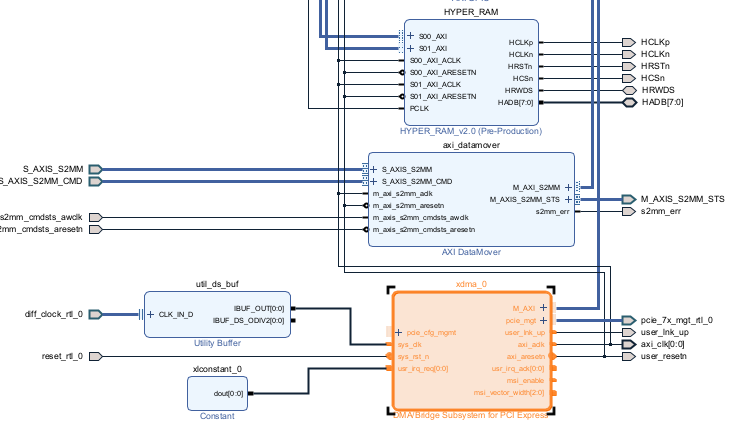

下図のオレンジ色のxdma_0ブロックがPCIeコア(無償のAXIバスマスタ)です。AXI_DataMover IP(無償)により、AXIバスに外部データを取り込んでHYPER_RAMブロック(弊社IP)に自動転送し、FPGAに接続している256MbitのHyperRAMにデータを蓄積できます。

PCIeコアがHYPER_RAMブロックからデータを読み出して、高速なPCIeでラズパイCM4に転送します。

CM4MBボードのサンプルプロジェクトを利用すれば、ユーザ仕様に適合したハードウエアは容易に開発が可能です。