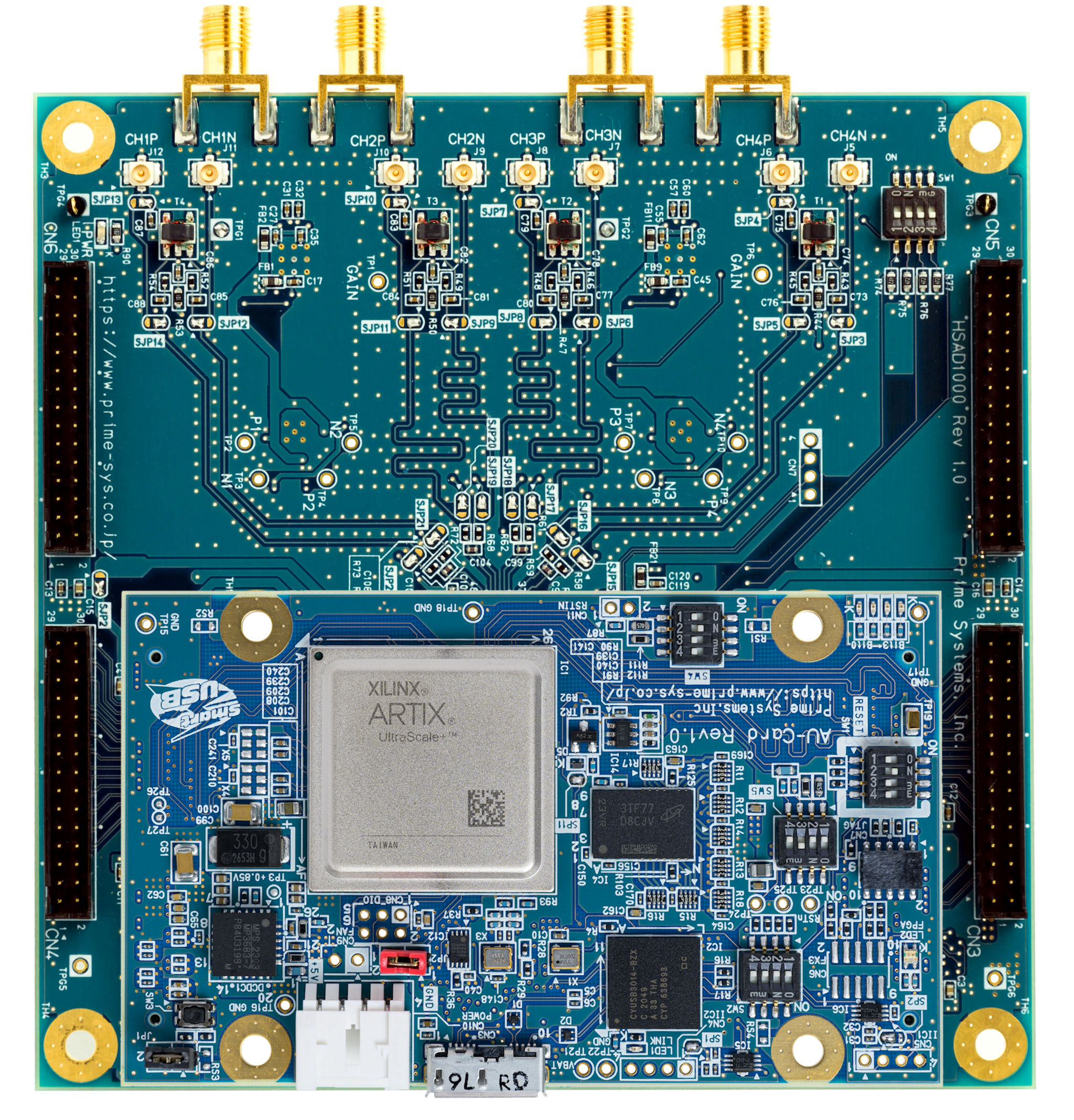

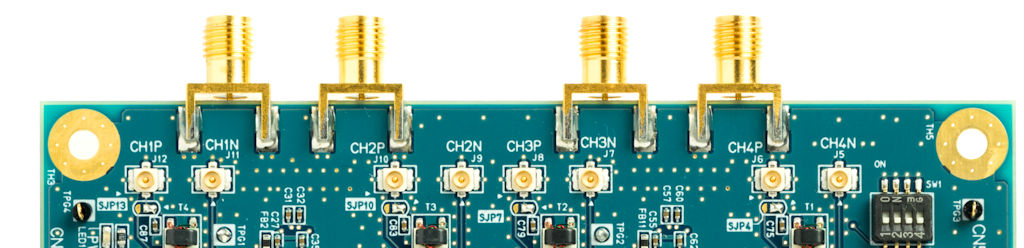

Option board: HSAD1000

4ch同時サンプリング 可変高速ADコンバータ

- AU-Card / SX-Card7 / AX-Card7 向けのAD変換オプションボードです。

- 有効チャネル数、分解能、サンプリング周波数をダイナミックに変更して運用できます。

- 最大ゲイン55dBのアンプとデジタルゲイン34dBで、高速・微小振幅の信号収集に対応。

- サンプルFPGA回路をカスタマイズして開発効率を向上できます。

- デザインサービスを利用して、アナログ回路を追加することもできます。

| 機能 | 1/2/4ch、8/12/14bit分解能、最大サンプリング900/640/105MSps (AnalogDevices社 HMCAD1520採用) |

| 型番と価格 | HSAD1000 \180,000(税別) |

| 資料 | ボード仕様(PDF) |

| 基板サイズと重量 | 110 x 110 (mm)、70g |

| FPGA-IF | AU-Cardと組み合わせた例  DDR LVDS(SERDES) 最大1,000Mbps。 ビットクロック、フレームクロック、データch x 8 FPGAと最大8GbpsでIFできます。アナログ入力チャネル数により、レートやデータch数が可変します。 (分解能 x サンプリング周波数 ÷ 1chあたりのLVDSデータレーン ≦ 1,000 Mbps が成り立つ設定で運用します。) |

| コネクタ | 104本のI/Oを2mmピッチ30ピンコネクタ(DF11シリーズ)4個に変換(LVDS設定可能) ※接続するFPGAボードの種類により、利用できるI/O数が変動します。 |

| アナログ入力仕様 | 4ch , 2Vpp, 50Ωインピーダンス、固定ゲイン(A=1) U.FLコネクタ シングルエンド/差動 対応 (シングルエンド時、入力信号≧4.5MHz) 4ch , 200mVpp, 50Ωインピーダンス、19dB~55dBゲイン、-3dB帯域幅max.100MHz SMAコネクタ シングルエンド専用  |

| コンフィギュラブル設定 | 分解能14bit:4ch同時サンプリング、最大105MSps 分解能12bit:1/2/4ch設定時、最大640M/320M/160MSps 分解能 8bit:2/4ch設定時、最大500M/250MSps (8/12bit設定時のみ、ch数を減じるとサンプリング周波数を高速にできます) デジタルゲイン:最大34dB、 アナログゲインと合わせて89dB設定での運用が可能です。 |

| サンプリングクロック設定 | 4極ディップスイッチにより、4種類のプリプログラムされた周波数を選択可能です。 100/105/500/640 MHz FPGAボードとI2C接続して、任意の周波数をレジスタ設定可能(電源断で揮発) FPGAボードとI2C接続して、任意の周波数をE2PROMにプログラム可能(不揮発) 製品出荷時にご希望の周波数をプログラムするサービスを提供 |